# High-Resolution ADC Using Delta-Sigma Architectures

**DESIGN DOCUMENT**

Released March 2, 2018

**Client:** Professors Geiger and Chen

**Faculty Advisor:** Dr. Randall Geiger

### **Team Members:**

Caroline Alva Tyler Archer Caleb Davidson Mahmoud Gshash Josh Rolles

## Table of Contents

| 1. Frontal Material                              | .2 |

|--------------------------------------------------|----|

| 1.1. List of Figures                             | .2 |

| 1.2. List of Equations                           | .2 |

| 1.3. List of Symbols                             | .2 |

| 1.4. List of Definitions                         | .2 |

| 2. Introductory Material                         | •3 |

| 2.1. Acknowledgement                             | •3 |

| 2.2. Problem Statement                           | .3 |

| 2.3. Operating Environment                       | .3 |

| 2.4. Intended Users and Intended Uses            | 3  |

| 2.5. Assumptions and Limitations                 | •4 |

| 2.6. Expected End Product and Other Deliverables | 4  |

| 3. Specifications and Analysis                   | •4 |

| 3.1. Approach                                    | •4 |

| 3.2. Temperature Sensor                          | •5 |

| 3.3. Clock                                       | 6  |

| 3.4. Delta-Sigma Modulator                       | .6 |

| 3.4.1. Differencing Amplifier                    | .7 |

| 3.4.2. Integrator                                |    |

| 3.4.3. Switched Capacitor                        | .7 |

| 3.4.4. Comparator                                | .8 |

| 3.4.5. DAC                                       | .9 |

| 3.5. Digital Decimator                           | 0  |

| 4. Testing and Implementation                    | 0  |

| 4.1. Interface Specifications                    | 10 |

| 4.1.1. Decimator                                 | 10 |

| 4.2. Hardware/Software                           | 10 |

| 4.2. Comparator                                  | 0  |

| 4.2. Decimator                                   | 10 |

| 4.3. Process                                     | 11 |

| 4.3.1. Comparator                                | 11 |

| 4.3.2. Decimator                                 | 11 |

| 5. Closing Materials                             | 12 |

| 5.1. Closing Summary1                            | 2  |

| 5.2. References                                  | 12 |

|                                                  |    |

## 2 Frontal Material

#### 1.1 LIST OF FIGURES

| Figure 3.1: Delta-Sigma ADC Block Diagram            |

|------------------------------------------------------|

| Figure 3.2: Temperature Sensor Structure             |

| Figure 3.3: Clock Generating Circuit                 |

| Figure 3.4: Block Diagram of Modulator               |

| Figure 3.5: Differential Op Amp Circuit              |

| Figure 3.6: Integrator                               |

| Figure 3.7: Switched Capacitor Circuit               |

| Figure 3.8: One-bit ADC (Comparator Circuit)         |

| Figure 3.9: One-bit ADC (Dynamic Comparator Circuit) |

| Figure 3.10: One-bit DAC Circuit                     |

| Figure 4.1: Output Testing of 1-Bit ADC11            |

#### **1.2 LIST OF EQUATIONS**

| Equation 3.1: Diode Current Equation                     | 5 |

|----------------------------------------------------------|---|

| Equation 3.2: Temperature Sensor Output Voltage Equation | 5 |

#### 1.3 LIST OF SYMBOLS

- Id Diode Current

- Iss Diode Reverse Saturation Current

- Vd Voltage Across a Diode

- Vt Thermal Voltage

- K Boltzmann's Constant

- T Temperature

- q Electron Charge

- n Number of Diodes

#### **1.4 LIST OF DEFINITIONS**

Integrated circuit (IC) - an electronic circuit formed on a piece of semiconducting material.<sup>1</sup>

- Analog to digital converter (ADC) an electronic device that converts an analog signal to a digital signal without altering its essential content.<sup>2</sup>

- Throttle control the operation speed of a circuit, and therefore its heat dissipation rate.

- **Sample** reduce a continuous-time signal to a discrete-time signal by collecting a series of its values at regularly spaced intervals.<sup>3</sup>

- **Resolution** the number of discrete output values an ADC can produce over the range of analog input values.<sup>4</sup>

- Delta-sigma ADC an ADC that produces a high-resolution output signal using oversampling techniques.<sup>5</sup>

- DAC an electronic device that converts a digital signal to an analog signal without altering its essential content.<sup>6</sup>

- Modulator an electronic device that varies one or more properties of a periodic waveform.<sup>7</sup>

- **Digital Filter** a system that performs mathematical operations on a discrete-time signal to modify certain aspects of that signal.<sup>8</sup>

- Digital Decimator a device that reduces the sampling rate of a digital signal.9

- **Parasitic Capacitance** a usually unwanted capacitance that exists between parts of electronic components or circuits because of their proximity to each other.<sup>10</sup>

- **Switched Capacitor Integrator** an electronic device that performs an integrating function using an operational amplifier and a switch-connected capacitor that acts as a current-limiting component.

- **Comparator** an electronic circuit that compares two voltages and outputs a digital signal indicating which voltage is larger.<sup>n</sup>

- Layout a representation of an integrated circuit using geometric shapes that correspond to the patterns of the materials that make up the physical integrated circuit.<sup>12</sup>

## 2 Introductory Material

#### 2.1 ACKNOWLEDGEMENT

This research and design is greatly supported by Dr. Randall Geiger. We'd like to thank Dr. Geiger for providing and continuing to provide key insight and expertise that greatly assists our research. His contributions are crucial in ensuring our team fully comprehends the scale and knowledge of this project.

#### 2.2 PROBLEM STATEMENT

We rely heavily on various integrated circuits (IC) to perform as originally intended every day. Without these circuits, we would have a difficult time with typical day to day tasks. Heat can become a serious issue when talking about ICs. When these chips overheat, it can damage the circuit and cause it malfunction. There is a need for a method to throttle the circuit performance based on its temperature.

Our team has proposed to create an analog-to-digital converter (ADC) with an onboard temperature sensor to accurately display the current temperature of the IC. With this technology, we can monitor the temperature of an IC as it is being used within a system to ensure it doesn't overheat. Based on this reading, the IC would have a system to throttle its performance to allow proper temperature decrease.

#### 2.3 OPERATING ENVIRONMENT

Our circuit can be implemented with any IC as it is intended to monitor the temperature of that IC. With this, the operating environments will vary depending on the system they are implemented in. For most purposes, this will result in being used in a small, closed off environment.

#### 2.4 INTENDED USERS AND INTENDED USES

Our product is to be used by IC designers when designing new ICs. They will implement our system onboard the same IC they are currently designing. In addition to the IC designers, the circuit will be used in the field by whomever is assigned to monitor the temperature of the system.

Our product will be used to successfully and easily measure the temperature of an IC. Its output is intended to be monitored by either a person or a computer. Based on the output, the system will change in

performance to allow for maximum performance at ideal temperatures or throttled performance when temperatures rise above a certain threshold.

#### 2.5 ASSUMPTIONS AND LIMITATIONS

Assumptions:

• Each IC in a complete system is individually monitored

Limitations

- Area of the layout is no more than 180 µm x 100 µm

- Supply voltage is to be +/- 1.8 V

#### 2.6 EXPECTED END PRODUCT AND OTHER DELIVERABLES

The end product will have a full circuit designed within Cadence in a 180 nm process. Included in this will be a full layout and post layout simulation. This will be delivered by the first week of May 2018 so it can be sent out for fabrication.

The end product will be a fully fabricated IC with our ADC and temperature sensor onboard. This will be fabricated by MOSIS over the summer of 2018 to allow ample time to be completed. The fabrication will be completed by August 2018 to allow our team to test for functionality of the physical IC.

The end product will be biased with an external voltage supply either in a lab or a different portion of the system it is being used in. The voltage supply will operate at +/- 1.8 V.

## 3 Specifications and Analysis

#### 3.1 APPROACH

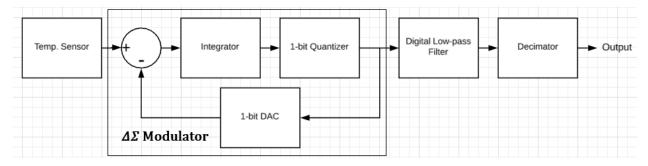

#### Figure 3.1: Delta-Sigma ADC Block Diagram

Our approach for this project is to implement an integrated circuit consisting of a temperature sensor and delta-sigma ADC using the top-level architecture shown in Figure 1. The design consists of a temperature sensor, a delta-sigma modulator, and a digital filter/decimator. The ADC is designed to take samples of the temperature sensor output at a rate of 102.4 kHz and output a 10-bit binary representation of the temperature at a data rate of 100 Hz.

#### 3.2 TEMPERATURE SENSOR

Since the quantity of interest is temperature, the sensor needs to be designed using a temperature dependent device. Given the equation of the diode current:

$$Id = Iss^{*} (e^{Vd/Vt} - 1)$$

(3.1)

The current through the diode is very temperature dependent, so by fixing the current, the voltage across the diode will change as vt changes, but how this property can be used?

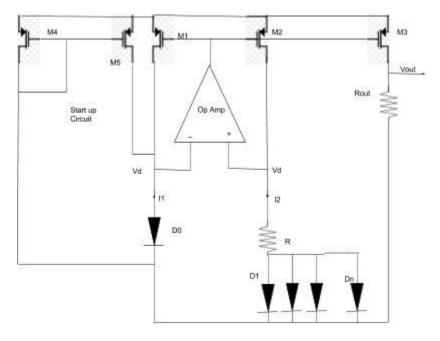

After doing some research, the following structure was found to give the best linear, and accurate temperature measurement:

Figure 3.2: Temperature Sensor Structure

$$Vout = \frac{KT}{q} * \frac{R_{out}}{R} * \ln(n)$$

(3.2)

In a CMOS process a diode can be realized by connecting the drain of a transistor to its gate.

#### 3.3 CLOCK

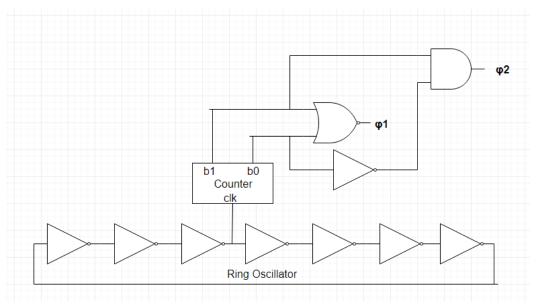

Figure 3,3: Clock Generating Circuit

A ring oscillator, which consists of a ring of seven inverters, generates the main clock, which has a frequency of 409.6 kHz. This is converted to  $\phi_1$  and  $\phi_2$  by the counter and logic gates, which assert  $\phi_1$  when the counter output is 10. Clocks  $\phi_1$  and  $\phi_2$  have are 180 degrees out of phase and each has a duty cycle of 25%, and a frequency of 102.4 kHz.

#### 3.4 DELTA-SIGMA MODULATOR

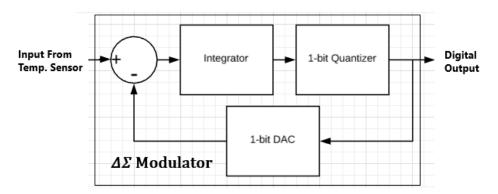

The delta-sigma modulator is the first of the two main parts of the delta-sigma ADC. The modulator takes the analog output of the temperature sensor as its input, and outputs a digital signal that contains the temperature data in the form of a 1-bit modulated pulse wave (Figure 4). In addition to converting an analog signal to a digital signal, the modulator implements noise shaping, in which much of the low-frequency quantization noise is moved to higher frequencies, so it can be low-pass filtered out in the next stage. The elimination of this quantization noise is responsible for the high accuracy of the delta-sigma ADC. The modulator contains a differencing block, plus three main functional blocks: an integrator, a 1-bit quantizer, and a 1-bit DAC.

Figure 3.4: Block Diagram of Modulator

#### 3.4.1 DIFFERENCING AMPLIFIER

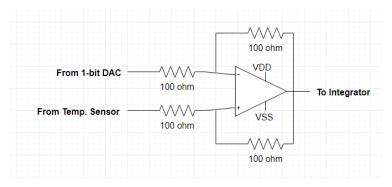

The differencing amplifier functions to subtract the feedback signal coming from the 1-bit DAC from the temperature sensor input before the signal is input to the integrator. It consists of a differential op amp circuit (Figure 3.5).

Figure 3.5: Differential Op Amp Circuit

#### 3.4.2 INTEGRATOR

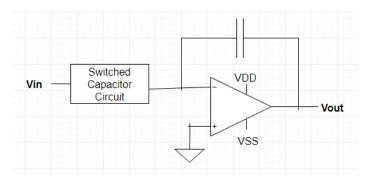

The integrator is the functional block that implements noise shaping. The voltage output of the integrator progresses in a negative or positive direction depending on the sign of the input voltage.<sup>5</sup> The slope of this progression depends on the magnitude of the input voltage. The integrator consists of an op amp with a feedback capacitor and a switched-capacitor input (Figure 3.6).

Figure 3.6: Integrator

#### 3.4.3 SWITCHED CAPACITOR

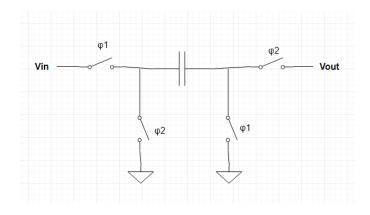

The switched capacitor circuit functions as both an input resistance to the integrator and as a sample-and-hold circuit. A schematic of the switched capacitor circuit is given in Figure 3.7.

Figure 3.7: Switched Capacitor Circuit

#### 3.4.4 COMPARATOR

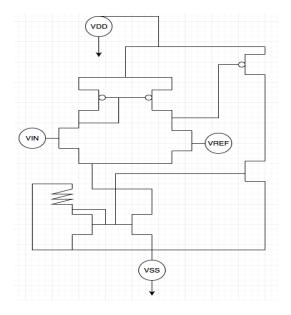

A one-bit ADC converts an analog signal into a one-bit digital output. A one-bit ADC can be modeled as a comparator circuit. A comparator compares two voltages, an input voltage and a reference voltage. If the input voltage is larger than the reference voltage the output of the comparator will be equivalent to VDD; if the input voltage is smaller than the reference voltage the output of the comparator will be equivalent to VSS. This comparator circuit is essentially a one-bit ADC because it takes in an analog input voltage and outputs a high 1 (VDD) or a low o (VSS).

A high gain two-stage operational amplifier with a differential input of a reference voltage was used as a one-bit ADC. The two-stage amplifier works as a sufficient comparator circuit. The team is still researching the benefits of using a dynamic comparator circuit, a clocked comparator. The dynamic comparator circuit only reads the input signal on the clock edge.

Figure 3.8: One-bit ADC (Comparator Circuit)

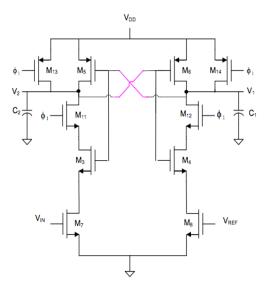

Figure 3.9: One-bit ADC (Dynamic Comparator Circuit)

#### 3.4.5 DAC

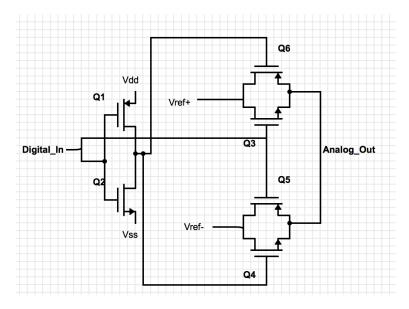

The 1-bit digital-to-analog converter (DAC) functions to take an analog input from the output of the comparator and convert it into a digital signal to output into the differencing block. This is done by using an inverter and two transmission gates to allow different reference voltages to pass. This configuration can be seen in Figure 3.10.

Figure 3.10: One-bit DAC Circuit

#### 3.5 DIGITAL DECIMATOR

Decimator and Low-pass digital filters:

A design choice has been made to look into a sinci filtration system as the design does not seem to need the complexity of widepass or sinc<sub>3</sub> or sinc<sub>5</sub> filtration system. In order to implement the sinci filter we will have a moving average fsm which will take in input data and summate that data with the previous sample data. Then this will divide every 1024 clock cycles of data stored by the number of samples (1024) to produce an output data stream at 1024th the input data stream. This number of clock cycles was used to implement a counter in order to do the averaging functionality. Register files will give us storage capability, and will hold data until overwritten by new data or by other reset functionality

## 4 Testing and Implementation

#### 4.1 INTERFACE SPECIFICATIONS

#### 4.1.1 DECIMATOR

Interfacing between our Delta Sigma ADC and the outside world will be through a 10-bit parallel output pins on the outside of the package. This simplifies the design while greatly increasing potential chance of success, with easier testability.

#### 4.2 HARDWARE AND SOFTWARE

#### 4.2.1 1-BIT ADC

The comparator will be tested using Cadence ADE. Simulations will need to be done to verify the function of the circuit as a comparator, and the input signal swing. The input signal swing is necessary to insure the comparator circuit can read the output of the integrator filter. The input signal swing range, should include 48omV, this is the voltage offset of the integrator circuit.

#### 4.2.2 DECIMATOR

- We will be using a test probe station created for IC testing along with oscilloscopes, digital multimeters, our IC, oven and a power supply.

- The oscilloscope and digital multimeters give us the ability to read our output and ensure signal integrity.

- The power supply is necessary to power on the IC, and the IC is the device under test (DUT).

- A test probe station will allow us to ensure the device can be connected to these measurement devices.

- The oven will be able to accurately tell a reading of temperature so that we can determine if our conversion has adequate precision.

#### 4.3 PROCESS

#### 4.3.1 COMPARATOR

To test the input voltage a simulation will be done to find the gain of the comparator the function "ymax" will be used to maintain the maximum gain value. A variable will be assigned on the input voltage and a sweep using parameterize will be plotted. The gain will be the highest point in the graph and anything +/-3dB of the gain will be the range. The input voltages that lie within that range are within the input signal swing. To be successful 48omV must lie within that range.

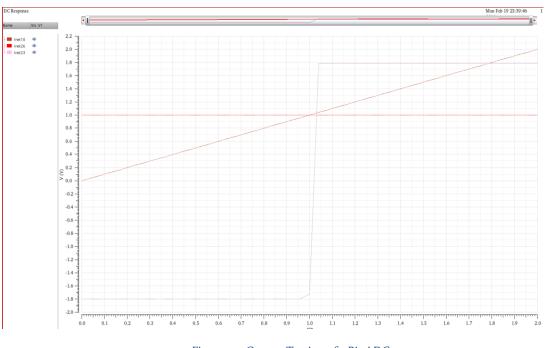

To test the functionality of the comparator circuit, a reference voltage is set and a design variable will be used as the input voltage. A DC sweep will be performed on the input voltage. The input voltage and the output voltage will be plotted. If the circuit works, as a comparator the output voltage will be equivalent to VSS, until the input voltage surpasses the value of the reference voltage, the output voltage will then be VDD.

Figure 4.1: Output Testing of 1-Bit ADC

The simulation results for the functionality are shown above. The circuit outputs a low until the input voltage surpasses the reference voltage and then the input output a high.

#### 4.3.2 DECIMATOR

Decimator and Low-pass digital filters:

To ensure that the decimator and low-pass digital filters are working properly, we will likely want an idea of the output of the modulator circuit. Once we can see that on a pin, we will be able to see the different between modulator output and filtered output.

- The low-pass filter and decimator must have proper characteristics of sampling and taking only 1/1024 of the samples given by the modulator.

- This can be achieved by measuring the modulator output and filtered output and comparing the two visually on an oscilloscope to ensure proper data is being sent with a constant temperature. Test criteria is that every 1024 samples of modulated input will return 1 sample of decimated output with accuracy of +/- 10 samples.

- To ensure that the filtration subsystem is working as expected we must take a set of data on output and store them as measurements. Once we determine the sampling rate of the output is correct, we can continue to ensure the filtration subsystem is giving correct data.

- That data must match the input modulator circuits' values within a margin of error of not more than 1 degree. The filtration should not change the output value, but rather remove quantization noise. This means we should see an analog input and digital output within 1 degree of accuracy. This can be seen on an oscilloscope with software to track data (Signal Express is a viable option).

## 5 Closing Material

#### 5.1 CLOSING SUMMARY

The goal of our project is to design a high-resolution data acquisition Integrated Circuit (IC), that converts physical real-life quantity into a digital representation. The circuit will be placed along with a temperature sensor in a chip to measure the chip's temperature. The accurate high-resolution measurement then used to allow the chip to throttle to prevent overheating. After weeks of researching data acquisition architectures, we used  $\Delta - \Sigma$  Analog to Digital Converter (ADC) architecture to realize our IC for it is known performance and robustness to noise. The output of the designed ADC will have 10-bits of resolution and will measure a temperature range from 20C to 60C with oversampling ratio of 1000 to 1, which means that for every 1000 sample at the input one sample will be given at the output. The  $\Delta - \Sigma$  ADC is comprised of many individual ICs such as amplifiers, switch capacitor circuits, integrators, and register files. All these components are designed at the transistor level, and tested rapidly, individually and combined, to make sure that the end product will be functional after fabrication.

#### **5.2 REFERENCES**

1. Google Search, Google, www.google.com.

- 2. "Analog-to-Digital Converter." Wikipedia, Wikimedia Foundation, 9 Feb. 2018, en.wikipedia.org.

- 3. "Sampling (Signal Processing)." Wikipedia, Wikimedia Foundation, 5 Feb. 2018, en.wikipedia.org.

- 4. "Analog-to-Digital Converter." Wikipedia, Wikimedia Foundation, 9 Feb. 2018, en.wikipedia.org.

- 5. Baker, Bonnie. "How Delta-Sigma ADCs Work, Part 1." www.ti.com.

- 6. "Digital-to-Analog Converter." Wikipedia, Wikimedia Foundation, 1 Feb. 2018, en.wikipedia.org.

- 7. "Modulation." Wikipedia, Wikimedia Foundation, 5 Feb. 2018, en.wikipedia.org.

- 8. "Digital Filter." Wikipedia, Wikimedia Foundation, 25 Nov. 2017, en.wikipedia.org.

- 9. "Decimation (Signal Processing)." Wikipedia, Wikimedia Foundation, 30 Jan. 2018, en.wikipedia.org.

- 10. "Parasitic Capacitance." Wikipedia, Wikimedia Foundation, 27 Jan. 2018, en.wikipedia.org.

- 11. "Comparator." Wikipedia, Wikimedia Foundation, 24 Jan. 2018, en.wikipedia.org.

12. "Integrated Circuit Layout." Wikipedia, Wikimedia Foundation, 23 Jan. 2018, en.wikipedia.org.